- Joined

- Nov 10, 2020

- Messages

- 12,207

- Likes

- 73,694

This article looks at BHARAT’s ongoing micro-controller & micro-processor R&D work in defence, space, telecom, IoT and other strategic sectors. Most of this R&D is funded by DRDO, MeitY, ISRO and related agencies (under direct/indirect control of the Government of India). While this has been the case so far, in recent years participation from academia & the private sector has increased substantially.

The need for Indian micro-controllers & micro-processors

In the early years, the need for micro-processors & micro-controllers was driven exclusively by the defence & space sectors. India’s 1st orbital launch vehicle was Indian Space Research Organisations’s (ISRO) Satellite Launch Vehicle (SLV) which was developed in the 1970s. In the early 1980s, the project director of the SLV program, Dr. APJ Abdul Kalam, was inducted into the Defence Research and Development Laboratory (DRDL) for the development of various guided missiles for the military.

The project was named the Integrated Guided Missile Development Program (IGDMP). From ballistic missiles to SAMs to ATGMs, IGDMP was an umbrella program for all kinds of guided missiles.

Understandably, India’s initial line up of guided missiles & launch vehicles used RF controlled solenoid driven actuation systems. As missile tech matured in the country demand for micro-controllers for actuation & micro-processors for On-Board Computers (OBCs) grew. Today, processors are increasingly common in a guided missiles & launch vehicles.

Thus design, fabrication, raw materials & component sourcing is becoming increasingly important to national security.

Differences between micro-controllers & micro-processors

A micro-controller is a very small, low-cost microcomputer designed to perform a specific task. These tasks could be displaying information, receiving remote signals, rotating the actuation motor to a particular angle etc.

The above table highlights the differences between a microprocessor and a microcontroller.[1]

The general micro-controller consists of the micro-processor, the memory (RAM, ROM, EPROM), Serial ports, peripherals (timers, counters), etc. All these systems are packaged into a single unit.[1]

In most missiles, a single powerful micro-processor is used along with a number of micro-controllers. The sensors on the missile sends data to the micro-processor which decides the action to be performed according to the mission requirement. The command from the micro-processor travels to the micro-controllers which manipulate the control surfaces/nozzle/TVCs to change/maintain course as needed.

Typically the motherboard containing the micro-processor & the daughter boards with the micro-controllers are stacked together to form what is known as the On-Board Computer (OBC). This stacking is done to minimize space taken up by the electronics inside a missile.

Missile Interface Unit of the Nirbhay missile.[2]

View attachment 132939

On-Board Computer of then Nirbhay missile. A processor from Intel is visible.[2]

Path of indigenisation for micro-controllers & micro-processors

The semi-conductor business is a critical & expensive business. The investments needed to have a foundry with state-of the art technology is in the range of hundreds of billions of US$. For a developing country like India setting up a foundry with the latest tech is not feasible.

Hence, the path chosen by the GoI to indigenise semi-conductors is as follows:

Indian efforts in semiconductors

Defence

DRDO has set up the Society for Integrated Circuit Technology & Applied Research (SITAR) & Advanced Numerical Research & Analysis Group (ANURAG) to design systems required for many DRDO projects. ANURAG was set up in the 1980s & SITAR in 2003. Prior to 2003, SITAR was a part of ITI Ltd. & played a lead role in development of ASIC for telecommunications in India.

They have 3 fabrication & packaging units :

DRDO states that the STARC facility is a 1 micron digital CMOS, DLM and MIL qualified fab with capability to process 150 mm wafers. MEMS fabrication facility also was established in 2012. MEMS Packaging & Testing Facility have been added in 2017.

GAETEC, on the other hand, started off by absorbing the process technology developed at DRDO’s Solid State Physics Laboratory (SSPL) & has been producing MMICs with 0.7 micron gate length MESFETs (G7a) and 0.5 micron gate length MESFETs (G5A) in GaAs Fab.

SSPL focused on standardizing semi-conductor production method, equipment & tooling to help GAETEC scale up manufacturing. Somewhere along the way they stopped investing in their Metal-Semiconductor Field Effect Transistor (MESFET) technology & went with the Standard Cell technology.

More recently a project entitled AlGaN/GaN High Electron Mobility Transistors: Material and Device Technology Development (BALRAM) was undertaken by Solid State Physics Laboratory (SSPL). Under this project SSPL developed & standardized production practices for GaN HEMTs for their use in the military & space sectors.

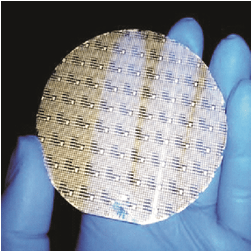

AlGaN/GaN HEMT processed wafer from the SSPL facility. Photo Credit: SSPL, DRDO.

SSPL currently serves as the primary silicon ingot & wafers production hub. SSPL has also developed facilities for epi-wafer growth and characterization, device simulation, device fabrication and DC, RF and load pull measurement etc.

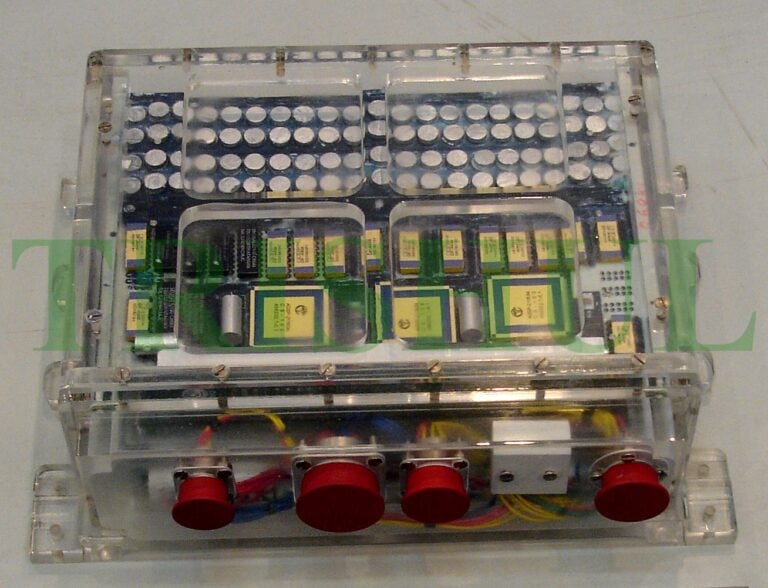

ANURAG designed & manufactured SoC chips for communication systems based on their own & imported processor cores. Photo from 2013. Photo Credit: Trishul blog

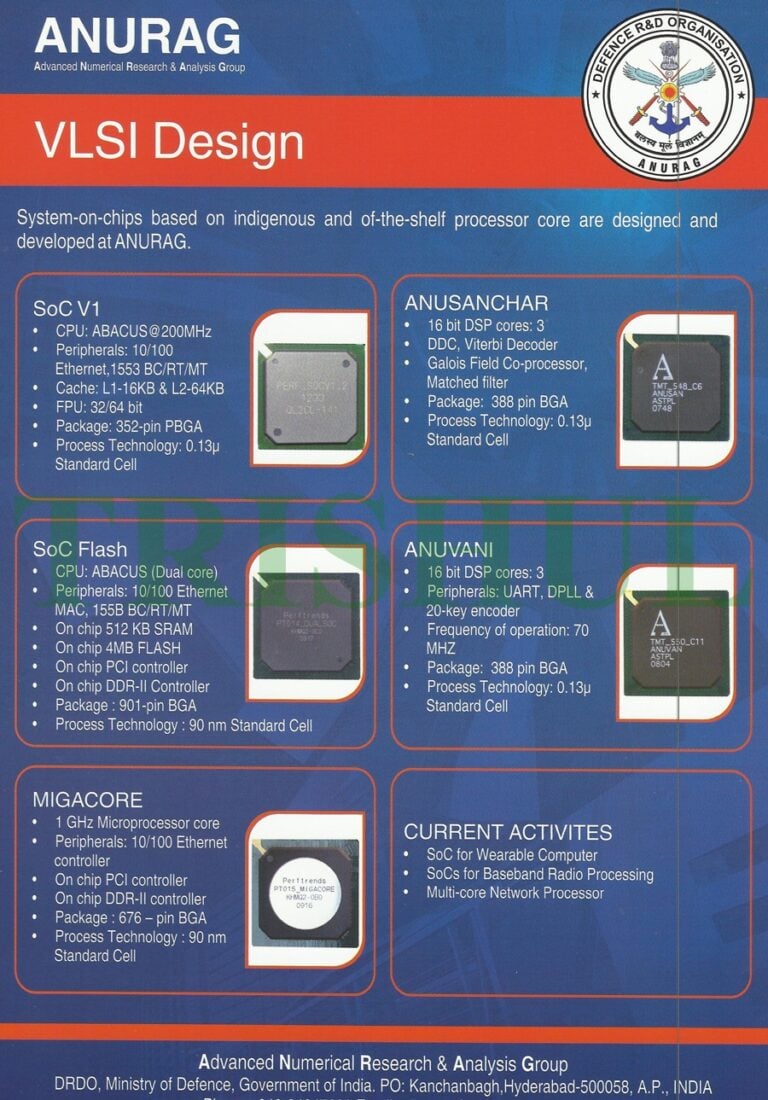

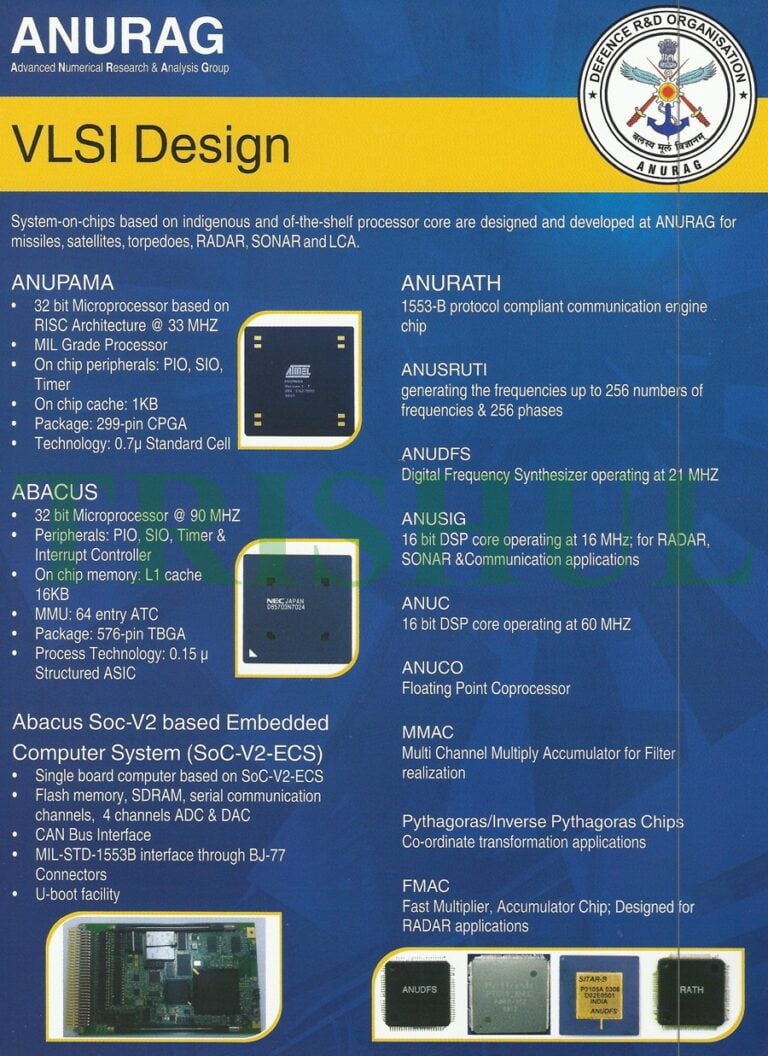

By 2013, GAETEC was able to operationalize Standard Cell technology of 130 & 90 nm node, assuming the poster above showcases GAETEC’s best capabilities at that time. The 90 nm Standard Cell tech could be used to fabricate Single/Dual Core 16/32/64 bit processors. Open source RISC architecture was preferred over Intel’s proprietary x86 architecture. The most powerful core available then was the 1 GHz MIGACORE.

Evidently the Ball Grid Array (BGA) was the preferred chip packaging technology. Various pin configuration (from 299 pins to 901 pins) were used depending on the size of the processor.

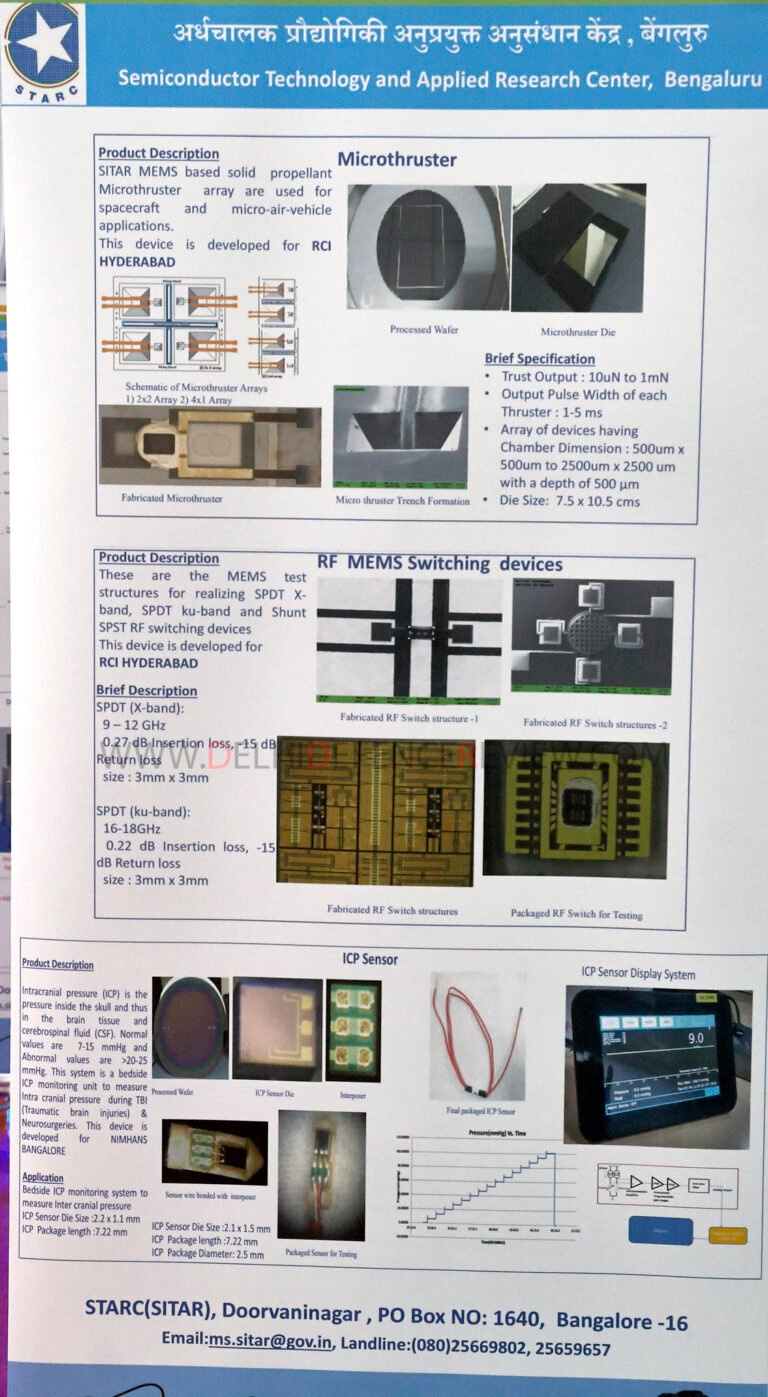

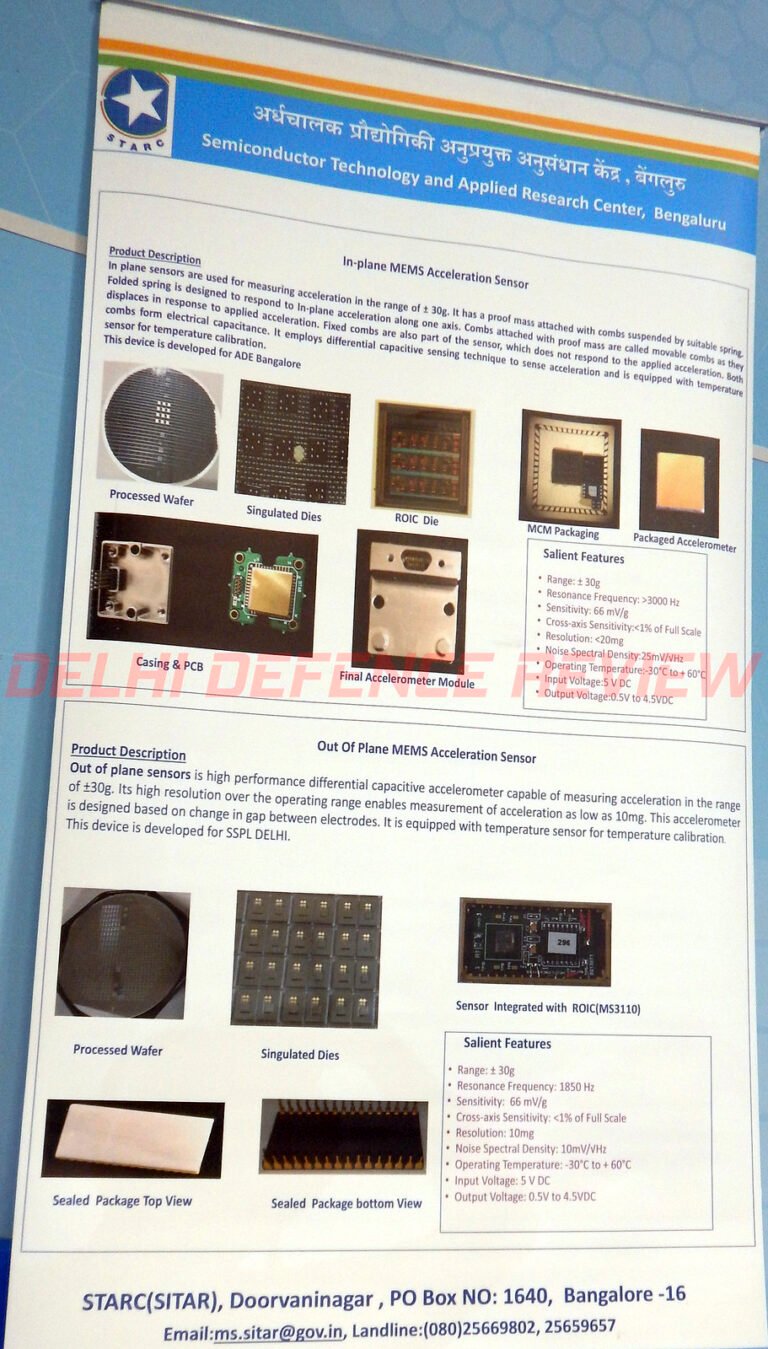

STARC showcased various sensors that are operational now in satellites, RF & IR guided missile seekers.

Evidently the Ball Grid Array (BGA) was the preferred chip packaging technology. Various pin configuration (from 299 pins to 901 pins) were used depending on the size of the processor.

STARC showcased various sensors that are operational now in satellites, RF & IR guided missile seekers.

STARC made MEMS based micro-thruster for space applications & RF switching systems. The RF switching systems are for X-band & Ku-band radar seekers. Photo Credit: DDR

STARC made pressure transducer for underwater applications. Photo Credit: DDR

The current production capacity of the GAETEC & STARC facilities are unknown. In the media, over the last decade, there has been an information gap about the developments in the defence semi-conductor realm. At least some of that is driven by a deliberate policy of secrecy.

While, in the early 2010s, there was some talk of DRDO developing more advanced fabrication technology; there were hardly any specifics mentioned & the news died down.

In DefExpo-2018 DRDO displayed an S-band Radio Frequency Integrated Circuit (RFIC) fabricated at IHP’s 250 nm fab in Germany. They also showcased a ADC+Baseband radio chip fabricated at UMC’s 65 nm fab in Taiwan. These chips are meant for a Digital Multi-media Broadcast (DMB) SATCOM terminal. Photo Credit: DDR

To be continued.

The need for Indian micro-controllers & micro-processors

In the early years, the need for micro-processors & micro-controllers was driven exclusively by the defence & space sectors. India’s 1st orbital launch vehicle was Indian Space Research Organisations’s (ISRO) Satellite Launch Vehicle (SLV) which was developed in the 1970s. In the early 1980s, the project director of the SLV program, Dr. APJ Abdul Kalam, was inducted into the Defence Research and Development Laboratory (DRDL) for the development of various guided missiles for the military.

The project was named the Integrated Guided Missile Development Program (IGDMP). From ballistic missiles to SAMs to ATGMs, IGDMP was an umbrella program for all kinds of guided missiles.

Understandably, India’s initial line up of guided missiles & launch vehicles used RF controlled solenoid driven actuation systems. As missile tech matured in the country demand for micro-controllers for actuation & micro-processors for On-Board Computers (OBCs) grew. Today, processors are increasingly common in a guided missiles & launch vehicles.

Thus design, fabrication, raw materials & component sourcing is becoming increasingly important to national security.

Differences between micro-controllers & micro-processors

A micro-controller is a very small, low-cost microcomputer designed to perform a specific task. These tasks could be displaying information, receiving remote signals, rotating the actuation motor to a particular angle etc.

The above table highlights the differences between a microprocessor and a microcontroller.[1]

The general micro-controller consists of the micro-processor, the memory (RAM, ROM, EPROM), Serial ports, peripherals (timers, counters), etc. All these systems are packaged into a single unit.[1]

In most missiles, a single powerful micro-processor is used along with a number of micro-controllers. The sensors on the missile sends data to the micro-processor which decides the action to be performed according to the mission requirement. The command from the micro-processor travels to the micro-controllers which manipulate the control surfaces/nozzle/TVCs to change/maintain course as needed.

Typically the motherboard containing the micro-processor & the daughter boards with the micro-controllers are stacked together to form what is known as the On-Board Computer (OBC). This stacking is done to minimize space taken up by the electronics inside a missile.

Missile Interface Unit of the Nirbhay missile.[2]

View attachment 132939

On-Board Computer of then Nirbhay missile. A processor from Intel is visible.[2]

Path of indigenisation for micro-controllers & micro-processors

The semi-conductor business is a critical & expensive business. The investments needed to have a foundry with state-of the art technology is in the range of hundreds of billions of US$. For a developing country like India setting up a foundry with the latest tech is not feasible.

Hence, the path chosen by the GoI to indigenise semi-conductors is as follows:

- Import generic processors from Intel et al and build systems around them. Acquire experience in system design, coding, algorithms etc.

- Acquire expertise in simple & eventually complex VLSI chip designs. Have them fabricated abroad. Build systems around those custom built chips.

- Set up some fabrication ability in the country. Nothing very expensive. But good enough to make most low-mid capacity chips that are needed in quantity.

- Once sufficient skills have been acquired in ship fabrication, move up the ladder. Upgrade the production facilities for both better technology node & production capacity.

Indian efforts in semiconductors

Defence

DRDO has set up the Society for Integrated Circuit Technology & Applied Research (SITAR) & Advanced Numerical Research & Analysis Group (ANURAG) to design systems required for many DRDO projects. ANURAG was set up in the 1980s & SITAR in 2003. Prior to 2003, SITAR was a part of ITI Ltd. & played a lead role in development of ASIC for telecommunications in India.

They have 3 fabrication & packaging units :

- Semiconductor Technology & Applied Research Centre (STARC) at Bangalore. A majority of the critical RF, MEMS sensors & some micro-controllers are made in this facility.

- Gallium Arsenide Enabling Technology Centre (GAETEC) at Hyderabad. Most of the micro-processors & micro-controllers used in military communication equipment and the OBCs of Indian aircrafts, missiles & munitions are made by GAETEC.

- A smaller prototyping fab at SITAR probably using a 100 nm CMOS technology.[10]

DRDO states that the STARC facility is a 1 micron digital CMOS, DLM and MIL qualified fab with capability to process 150 mm wafers. MEMS fabrication facility also was established in 2012. MEMS Packaging & Testing Facility have been added in 2017.

GAETEC, on the other hand, started off by absorbing the process technology developed at DRDO’s Solid State Physics Laboratory (SSPL) & has been producing MMICs with 0.7 micron gate length MESFETs (G7a) and 0.5 micron gate length MESFETs (G5A) in GaAs Fab.

SSPL focused on standardizing semi-conductor production method, equipment & tooling to help GAETEC scale up manufacturing. Somewhere along the way they stopped investing in their Metal-Semiconductor Field Effect Transistor (MESFET) technology & went with the Standard Cell technology.

More recently a project entitled AlGaN/GaN High Electron Mobility Transistors: Material and Device Technology Development (BALRAM) was undertaken by Solid State Physics Laboratory (SSPL). Under this project SSPL developed & standardized production practices for GaN HEMTs for their use in the military & space sectors.

AlGaN/GaN HEMT processed wafer from the SSPL facility. Photo Credit: SSPL, DRDO.

SSPL currently serves as the primary silicon ingot & wafers production hub. SSPL has also developed facilities for epi-wafer growth and characterization, device simulation, device fabrication and DC, RF and load pull measurement etc.

ANURAG designed & manufactured SoC chips for communication systems based on their own & imported processor cores. Photo from 2013. Photo Credit: Trishul blog

By 2013, GAETEC was able to operationalize Standard Cell technology of 130 & 90 nm node, assuming the poster above showcases GAETEC’s best capabilities at that time. The 90 nm Standard Cell tech could be used to fabricate Single/Dual Core 16/32/64 bit processors. Open source RISC architecture was preferred over Intel’s proprietary x86 architecture. The most powerful core available then was the 1 GHz MIGACORE.

Evidently the Ball Grid Array (BGA) was the preferred chip packaging technology. Various pin configuration (from 299 pins to 901 pins) were used depending on the size of the processor.

STARC showcased various sensors that are operational now in satellites, RF & IR guided missile seekers.

Evidently the Ball Grid Array (BGA) was the preferred chip packaging technology. Various pin configuration (from 299 pins to 901 pins) were used depending on the size of the processor.

STARC showcased various sensors that are operational now in satellites, RF & IR guided missile seekers.

STARC made MEMS based micro-thruster for space applications & RF switching systems. The RF switching systems are for X-band & Ku-band radar seekers. Photo Credit: DDR

STARC made pressure transducer for underwater applications. Photo Credit: DDR

The current production capacity of the GAETEC & STARC facilities are unknown. In the media, over the last decade, there has been an information gap about the developments in the defence semi-conductor realm. At least some of that is driven by a deliberate policy of secrecy.

While, in the early 2010s, there was some talk of DRDO developing more advanced fabrication technology; there were hardly any specifics mentioned & the news died down.

In DefExpo-2018 DRDO displayed an S-band Radio Frequency Integrated Circuit (RFIC) fabricated at IHP’s 250 nm fab in Germany. They also showcased a ADC+Baseband radio chip fabricated at UMC’s 65 nm fab in Taiwan. These chips are meant for a Digital Multi-media Broadcast (DMB) SATCOM terminal. Photo Credit: DDR

To be continued.